Intel B940 Datasheet Page 207

- Page / 360

- Table of contents

- BOOKMARKS

Rated. / 5. Based on customer reviews

Datasheet, Volume 2 207

Processor Configuration Registers

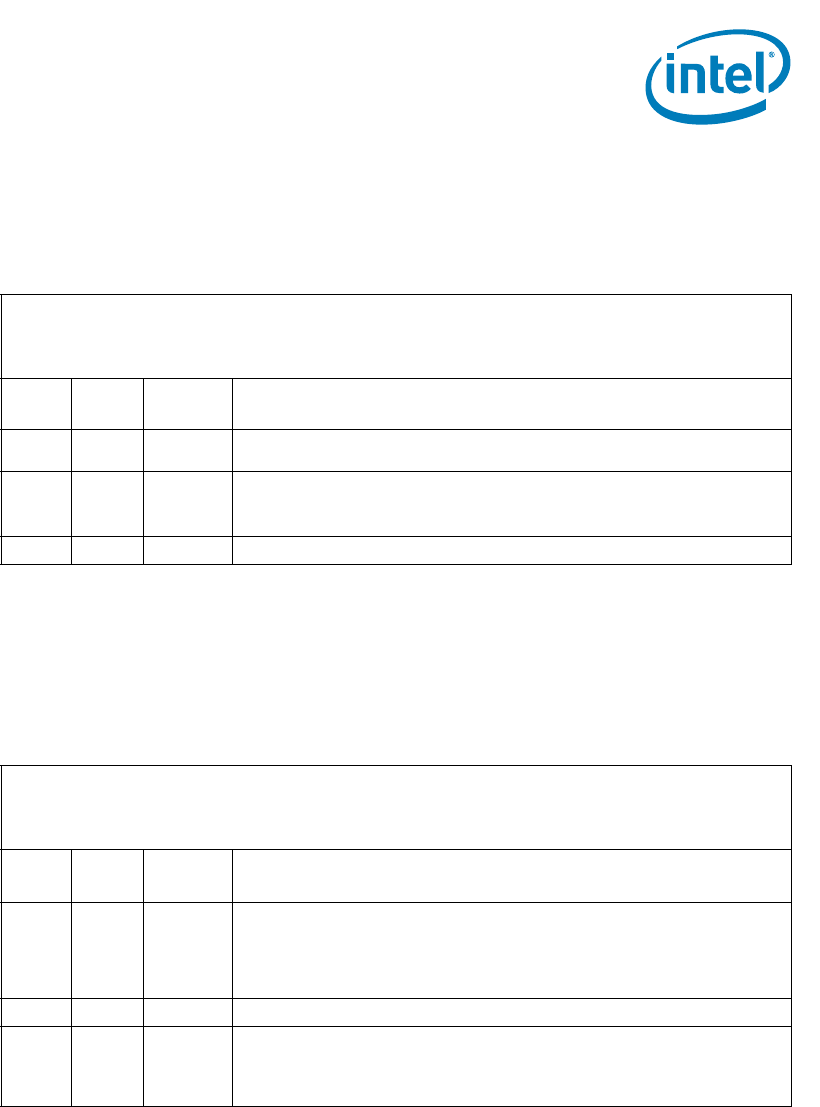

2.15.20 IQT_REG—Invalidation Queue Tail Register

Register indicating the invalidation tail head. This register is treated as reserved by

implementations reporting Queued Invalidation (QI) as not supported in the Extended

Capability register.

2.15.21 IQA_REG—Invalidation Queue Address Register

Register to configure the base address and size of the invalidation queue. This register

is treated as reserved by implementations reporting Queued Invalidation (QI) as not

supported in the Extended Capability register. When supported, writing to this register

causes the Invalidation Queue Head and Invalidation Queue Tail registers to be reset to

0h.

B/D/F/Type: 0/0/0/VC0PREMAP

Address Offset: 88–8Fh

Reset Value: 0000000000000000h

Access: RO

Bit Attr

Reset

Value

Description

63:19 RO

00000000

0000h

Reserved

18:4 RO 0000h

Queue Tail (QT)

This field specifies the offset (128-bit aligned) to the invalidation queue for

the command that will be written next by software.

3:0 RO 0h Reserved

B/D/F/Type: 0/0/0/VC0PREMAP

Address Offset: 90–97h

Reset Value: 0000000000000000h

Access: RW, RO

Bit Attr

Reset

Value

Description

63:12 RW

00000000

00000h

Invalidation Queue Base Address (IQA)

This field points to the base of 4 KB aligned invalidation request queue.

Hardware ignores and not implement bits 63:HAW,where HAW is the host

address width. Reads of this field return the value that was last programmed

to it.

11:3 RO 000h Reserved

2:0 RW 0h

Queue Size (QS)

This field specifies the size of the invalidation request queue. A value of X in

this field indicates an invalidation request queue of (X+1) 4 KB pages. The

number of entries in the invalidation queue is 2(X + 8).

- Datasheet – Volume 2 1

- Legal Lines and Disclaimers 2

- Contents 3

- 4 Datasheet, Volume 2 4

- Datasheet, Volume 2 5 5

- 6 Datasheet, Volume 2 6

- Datasheet, Volume 2 7 7

- 8 Datasheet, Volume 2 8

- Datasheet, Volume 2 9 9

- 10 Datasheet, Volume 2 10

- Datasheet, Volume 2 11 11

- Revision History 12

- 1 Introduction 13

- Introduction 14

- 2 Processor Configuration 15

- 2.2 System Address Map 17

- 18 Datasheet, Volume 2 18

- 2.2.1 Legacy Address Range 19

- Datasheet, Volume 2 21 21

- 2.2.2.2 TSEG 22

- 2.2.2.5 Pre-allocated Memory 23

- 2.2.2.7 Intel 24

- Management Engine (Intel 24

- ME) UMA 24

- Datasheet, Volume 2 25 25

- 2.2.2.10 High BIOS Area 26

- Datasheet, Volume 2 27 27

- 2.2.3.1 Programming Model 28

- HOST/SYSTEM VIEW 29

- PHYSICAL MEMORY 29

- (DRAM CONTROLLER VIEW) 29

- Datasheet, Volume 2 33 33

- 34 Datasheet, Volume 2 34

- 2.2.9 I/O Address Space 35

- 36 Datasheet, Volume 2 36

- Datasheet, Volume 2 37 37

- 2.4 Configuration Mechanisms 38

- Datasheet, Volume 2 39 39

- 40 Datasheet, Volume 2 40

- Datasheet, Volume 2 41 41

- 42 Datasheet, Volume 2 42

- Datasheet, Volume 2 43 43

- 2.6 I/O Mapped Registers 44

- 2.7.6 CC—Class Code Register 49

- TXT Lockable 54

- 1:0 to 11b 56

- 4) from 58

- B0h, bits 15:4) 58

- 2.8 MCHBAR Registers 66

- 00h RW 67

- Register Symbol Register Name 67

- 208–209h 73

- 20A–20Bh 74

- 24D–24Fh 74

- 250-251h 75

- 252–255h 76

- 256–257h 77

- 258–25Ah 77

- 269–26Eh 79

- 298–29Bh 82

- 29C–29Fh 84

- 2B4–2B7h 84

- 600–601h 86

- 602–603h 86

- 604–605h 86

- 64D–64Fh 88

- 650–651h 88

- 652–655h 89

- 656–657h 90

- 658–65Ah 90

- 660–663h 91

- 6B4–6B7h 93

- C20–C27h 94

- 1001–1002h 94

- 1004–1005h 95

- 101E–101Fh 100

- Register 107

- 10EC–10EDh 108

- 2C20–2C22h 109

- 2.9 EPBAR Registers 110

- 2.10 PCI Device 1 Registers 115

- PCI device 117

- Port Command Register 140

- 11:10 RW-O 11b 143

- OS's during run time 155

- 104–107h 156

- 108–10Bh 157

- 10C–10Dh 157

- 110–113h 158

- 23 RO 0b Reserved 158

- 114–117h 158

- 11A–11Bh 159

- 2.12 DMIBAR Registers 161

- Declaration Capability 169

- 2.13.6 CC—Class Code Register 177

- Range Address Register 179

- GMADR register 180

- 2.14 Device 2 I/O Registers 183

- 100–107h 211

- 108–10Fh 212

- 200–20Fh 214

- F00–F03h 215

- F04–F07h 216

- Dedication 217

- F08–F0Bh 218

- FFC–FFFh 219

- 2.16 DMI VC1 REMAP Registers 221

- 2.17.2 GFXPLL1—GFX PLL BIOS 254

- 2.18 GFXVTBAR Registers 255

- Address Register 281

- 2.19 PCI Device 6 Registers 288

- 2.19.45 RSTS—Root Status 327

- 2.21 Intel 332

- Specific Registers 332

- 110–117h 333

- 330–337h 333

- Lower Half Register 334

- Upper Half Register 334

- QuickPath Architecture 335

- System Address Decode 335

- Register Description 335

- QPI Link 0 Registers 340

- QPI Physical 0 Registers 341

- 3.4 PCI Standard Registers 342

- 3.4.4 CCR—Class Code Register 344

- Identification Register 345

- 3.4.7 PCICMD—Command Register 346

- 3.5.1 MAX_RTIDS 349

- 3.6.1 SAD_PAM0123 349

- 3.6.2 SAD_PAM456 351

- 3.6.3 SAD_HEN 352

- 3.6.4 SAD_SMRAM 353

- 3.6.5 SAD_PCIEXBAR 354

- 3.7 Intel 356

- QPI Link Registers 356

- 3.8 Intel 357

- QPI Physical Layer Registers 357

- 360 Datasheet, Volume 2 360

(292 pages)

(292 pages)

Comments to this Manuals