Intel E3 User Manual Page 24

- Page / 116

- Table of contents

- BOOKMARKS

Rated. / 5. Based on customer reviews

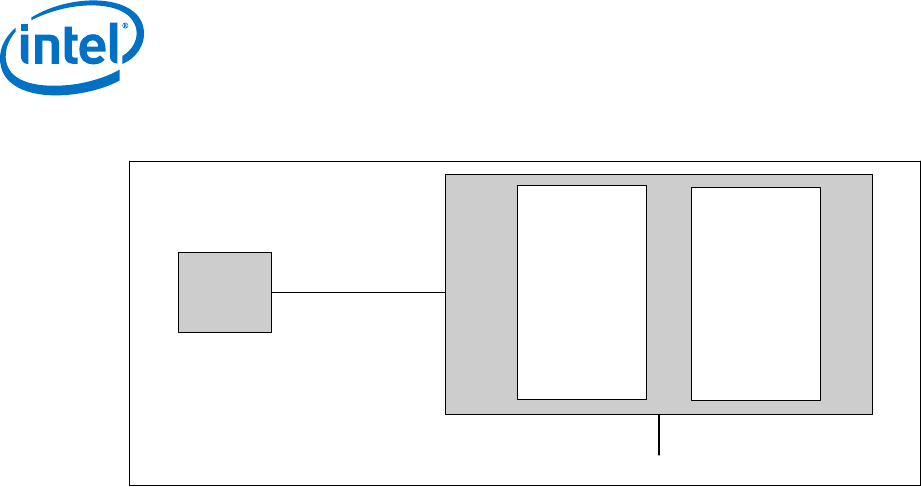

Figure 3. PCI Express* Related Register Structures in the Processor

PCI-PCI

Bridge

representing

root PCI

Express ports

(Device 1 and

Device 6)

PCI

Compatible

Host Bridge

Device

(Device 0)

PCI

Express*

Device

PEG0

DMI

PCI Express* extends the configuration space to 4096 bytes per-device/function, as

compared to 256 bytes allowed by the conventional PCI specification. PCI Express*

configuration space is divided into a PCI-compatible region (that consists of the first

256 bytes of a logical device's configuration space) and an extended PCI Express*

region (that consists of the remaining configuration space). The PCI-compatible region

can be accessed using either the mechanisms defined in the PCI specification or using

the enhanced PCI Express* configuration access mechanism described in the PCI

Express* Enhanced Configuration Mechanism section.

The PCI Express* Host Bridge is required to translate the memory-mapped PCI

Express* configuration space accesses from the host processor to PCI Express*

configuration cycles. To maintain compatibility with PCI configuration addressing

mechanisms, it is recommended that system software access the enhanced

configuration space using 32-bit operations (32-bit aligned) only. See the PCI Express

Base Specification for details of both the PCI-compatible and PCI Express* Enhanced

configuration mechanisms and transaction rules.

PCI Express* Lanes Connection

The following figure demonstrates the PCIe* lane mapping.

Processor—Interfaces

Intel

®

Xeon

®

Processor E3-1200 v3 Product Family

Datasheet – Volume 1 of 2 June 2013

24 Order No.: 328907-001

- Processor E3-1200 v3 1

- Product Family 1

- 2 Order No.: 328907-001 2

- Contents 3

- Revision History 8

- 1.0 Introduction 9

- 1.1 Supported Technologies 10

- 1.2 Interfaces 11

- 1.3 Power Management Support 11

- 1.5 Package Support 12

- 1.6 Terminology 12

- 1.7 Related Documents 15

- 2.0 Interfaces 17

- 2.1.3.2 Intel 21

- Fast Memory Access (Intel 21

- FMA) Technology Enhancements 21

- 2.1.3.3 Data Scrambling 21

- 2.2 PCI Express* Interface 22

- 2.4 Processor Graphics 27

- Source Device Sink Device 32

- HDMI Source 33

- HDMI Sink 33

- 2.7 Intel 36

- <10pF/Node 37

- 3.0 Technologies 38

- 3.2 Intel 42

- Technology) 43

- 3.8 Intel 46

- 64 Architecture x2APIC 46

- Execute Disable Bit 47

- 4.0 Power Management 48

- States Supported 49

- Enhanced Intel 50

- SpeedStep 50

- Technology Key Features 50

- Thread 0 Thread 1 51

- Core 0 State 51

- Core N State 51

- Processor Package State 51

- C1 C1E C7C6C3 52

- 4.2.4 Core C-State Rules 53

- Package C-States 54

- 4.3.2.3 Dynamic Power-Down 60

- CCIO_TERM 61

- 5.0 Thermal Management 63

- Measure T 64

- (DTS) 2.0 66

- 5.4 Intel 67

- Thermal Specifications 67

- 5.5 Processor Temperature 69

- Adaptive Thermal Monitor 69

- THERMTRIP# Signal 72

- 5.8 Digital Thermal Sensor 73

- 5.9 Intel 74

- 5.9.2 Package Power Control 75

- 5.9.3 Turbo Time Parameter 75

- 6.0 Signal Description 77

- Table 24. Memory Channel B 78

- 6.8 Testability Signals 82

- 6.10 Power Sequencing 84

- 6.11 Processor Power Signals 84

- 6.12 Sense Pins 84

- 7.2 Power and Ground Lands 86

- Voltage Identification (VID) 86

- 7.5 Signal Groups 91

- DC Specifications 93

- 8.7 Processor Markings 103

(405 pages)

(405 pages)

Comments to this Manuals