Intel i7-2960XM Datasheet Page 50

- Page / 98

- Table of contents

- BOOKMARKS

Rated. / 5. Based on customer reviews

Register Description

50 Datasheet

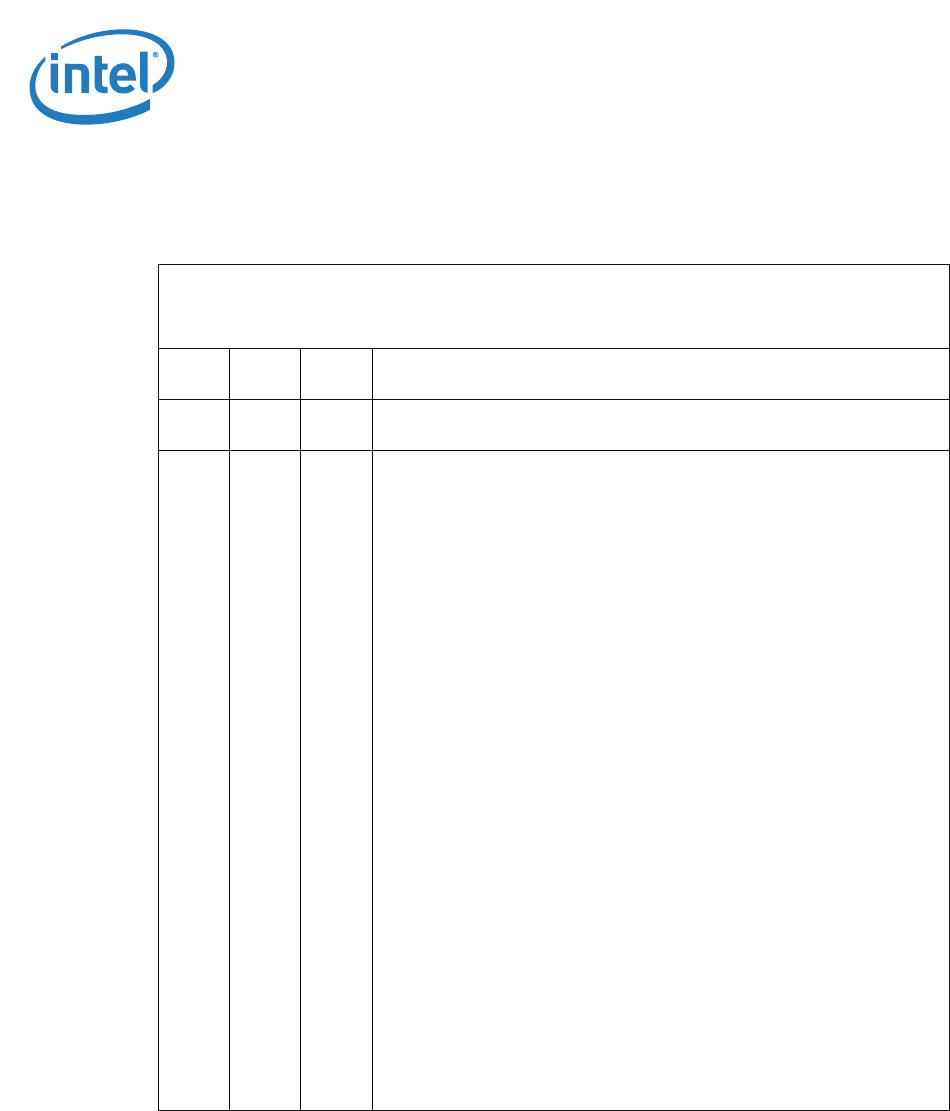

2.8.3 MC_SMI_SPARE_DIMM_ERROR_STATUS

SMI sparing DIMM error threshold overflow status register. This bit is set when the per-

DIMM error counter exceeds the specified threshold. The bit is reset by BIOS.

Device: 3

Function: 0

Offset: 50h

Access as a Dword

Bit Type

Reset

Value

Description

13:12 RW0C

0 REDUNDANCY_LOSS_FAILING_DIMM

The ID for the failing DIMM when redundancy is lost.

11:0 RW0C

0 DIMM_ERROR_OVERFLOW_STATUS

This 12-bit field is the per dimm error overflow status bits. The organization is

as follows:

If there are three or more DIMMS on the channel:

Bit 0 = DIMM 0 Channel 0

Bit 1 = DIMM 1 Channel 0

Bit 2 = DIMM 2 Channel 0

Bit 3 = DIMM 3 Channel 0

Bit 4 = DIMM 0 Channel 1

Bit 5 = DIMM 1 Channel 1

Bit 6 = DIMM 2 Channel 1

Bit 7 = DIMM 3 Channel 1

Bit 8 = DIMM 0 Channel 2

Bit 9 = DIMM 1 Channel 2

Bit 10 = DIMM 2 Channel 2

Bit 11 = DIMM 3 Channel 2

If there are one or two DIMMS on the channel:

Bit 0 = DIMM 0, Ranks 0 and 1, Channel 0

Bit 1 = DIMM 0, Ranks 2 and 3, Channel 0

Bit 2 = DIMM 1, Ranks 0 and 1, Channel 0

Bit 3 = DIMM 1, Ranks 2 and 3, Channel 0

Bit 4 = DIMM 0, Ranks 0 and 1, Channel 1

Bit 5 = DIMM 0, Ranks 2 and 3, Channel 1

Bit 6 = DIMM 1, Ranks 0 and 1, Channel 1

Bit 7 = DIMM 1, Ranks 2 and 3, Channel 1

Bit 8 = DIMM 0, Ranks 0 and 1, Channel 2

Bit 9 = DIMM 0, Ranks 2 and 3, Channel 2

Bit 10 = DIMM 1, Ranks 0 and 1, Channel 2

Bit 11 = DIMM 1, Ranks 2 and 3, Channel 2

- Datasheet, Volume 2 1

- Contents 3

- 4 Datasheet 4

- Datasheet 5 5

- 6 Datasheet 6

- Datasheet 7 7

- 8 Datasheet 8

- Revision History 9

- 10 Datasheet 10

- 1 Introduction 11

- Introduction 12

- 12 Datasheet 12

- 1.2 References 13

- 14 Datasheet 14

- 2 Register Description 15

- 2.3 Device Mapping 17

- Control Registers 24

- Address Registers 25

- Rank Registers 26

- Thermal Control Registers 27

- 2.5 PCI Standard Registers 36

- Identification Register 38

- Express space 39

- 2.6.1 SAD_PAM0123 41

- 2.6.2 SAD_PAM456 43

- 2.6.3 SAD_HEN 44

- 2.6.4 SAD_SMRAM 44

- 2.6.5 SAD_PCIEXBAR 45

- 19:6 RW 46

- 2:1 RW 46

- 2.7 Intel QPI Link Registers 47

- 2.8.2 MC_STATUS 49

- 13:12 RW0C 50

- 11:0 RW0C 50

- 2.8.4 MC_SMI_SPARE_CNTRL 51

- 2.8.5 MC_RESET_CONTROL 51

- 2.8.6 MC_CHANNEL_MAPPER 52

- 2.8.7 MC_MAX_DOD 53

- 2.8.8 MC_RD_CRDT_INIT 54

- 2.8.9 MC_CRDT_WR_THLD 55

- 2.8.10 MC_SCRUBADDR_LO 55

- 2.8.11 MC_SCRUBADDR_HI 56

- 29:28 RW 58

- 25:24 RW 58

- 21:20 RW 58

- 17:16 RW 58

- 13:12 RW 58

- Registers 59

- MC_CHANNEL_1_DIMM_INIT_CMD 60

- MC_CHANNEL_2_DIMM_INIT_CMD 60

- MC_CHANNEL_1_DIMM_INIT_PARAMS 61

- MC_CHANNEL_2_DIMM_INIT_PARAMS 61

- MC_CHANNEL_1_DIMM_INIT_STATUS 62

- MC_CHANNEL_2_DIMM_INIT_STATUS 62

- 2.10.5 MC_CHANNEL_0_DDR3CMD 63

- MC_CHANNEL_1_DDR3CMD 63

- MC_CHANNEL_2_DDR3CMD 63

- 3:2 RW 0 64

- 31:16 RW 0 64

- 15:0 RW 0 64

- 23:20 RW 0 65

- 19:16 RW 0 65

- 7:0 RW 0 65

- MC_CHANNEL_1_RANK_TIMING_A 66

- MC_CHANNEL_2_RANK_TIMING_A 66

- 18:15 RW 0 67

- 14:11 RW 0 67

- 10:7 RW 0 67

- 6:4 RW 0 68

- 3:1 RW 0 68

- MC_CHANNEL_1_RANK_TIMING_B 69

- MC_CHANNEL_2_RANK_TIMING_B 69

- 29:19 RW 0 70

- 18:9 RW 0 70

- 8:0 RW 0 70

- MC_CHANNEL_1_WAQ_PARAMS 75

- MC_CHANNEL_2_WAQ_PARAMS 75

- MC_CHANNEL_1_ADDR_MATCH 81

- MC_CHANNEL_2_ADDR_MATCH 81

- 31:0 RW 0 82

- 2:1 RW 0 82

- Datasheet 83 83

- Register Description 83

- 26:24 RW 0 87

- 23:0 RW 0 87

- 13:4 RW 0 90

- 3:0 RW 0 90

- 2.13 Memory Thermal Control 92

- Throttling (CLTT) 93

- 2.14.2 MC_DIMM_CLK_RATIO 98

(49 pages)

(49 pages)

Comments to this Manuals