Intel RH80532NC033256 Datasheet Page 50

- Page / 98

- Table of contents

- BOOKMARKS

Rated. / 5. Based on customer reviews

Mobile Intel

®

Celeron

®

Processor (0.13 µ) in

Micro-FCBGA and Micro-FCPGA Packages Datasheet

50 Datasheet 298517-006

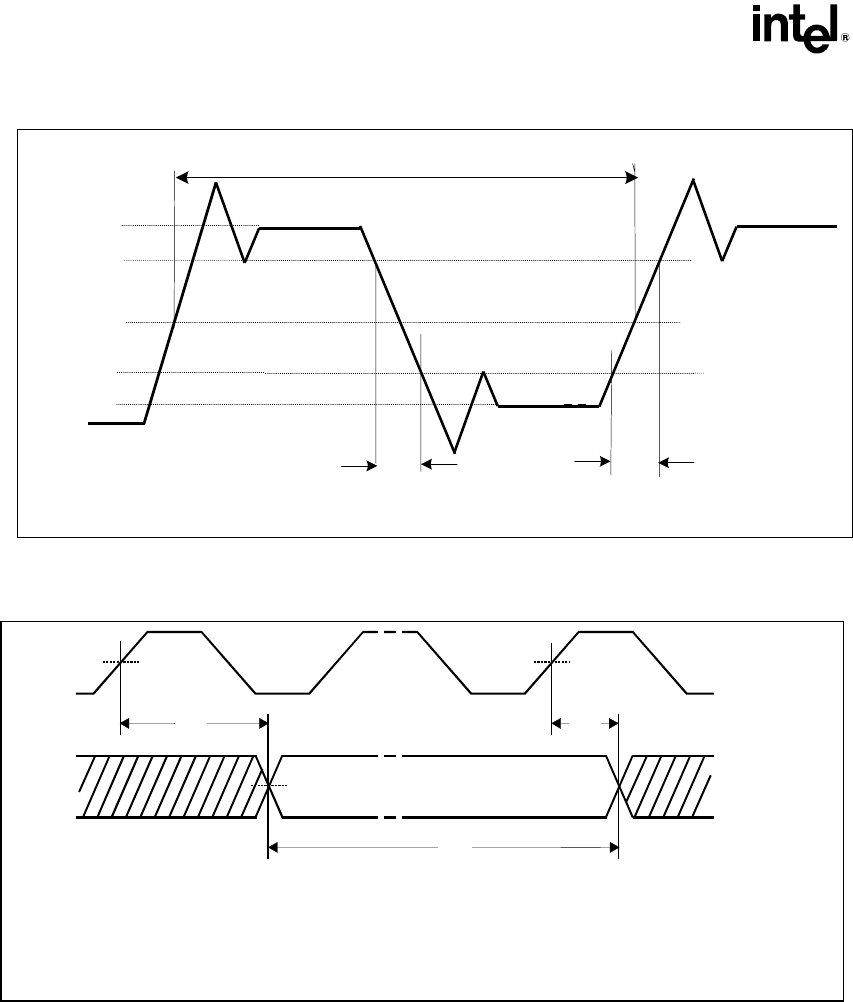

Figure 11. BCLK/BCLK# Waveform (Differential Mode)

0V

T6

T5

T1

V4

V5

V

IH_DIFF

V

Il_DIFF

Figure 12. Valid Delay Timings

CLK

Signal

T

X

T

x

T

PW

V Valid Valid

D0004-00

Vc Vc

NOTES:

T

x

= T7, T11, T29 (Valid Delay)

T

pw

= T14, T14B (Pulse Width)

V = V

REF

for AGTL signal group; 1.0V for CMOS, Open-drain, APIC, and TAP signal groups

Vc = Crossing point of BCLK rising edge and BCLK# falling edge for BCLK references (Differential Clock)

= 1.25V (Single Ended Clock)

- Mobile Intel 1

- Celeron 1

- Processor (0.13 µ) in 1

- Contents 3

- Figures 5

- Revision History 8

- Processor 9

- FCPGA Packages 9

- 1. Introduction 10

- 1.2 State of the Data 11

- 1.3 Terminology 11

- 1.4 References 12

- Features 13

- 2.2 Power Management 14

- 2.2.4 Quick Start State 15

- 2.2.6 Deep Sleep State 16

- 2.3 AGTL Signals 17

- EAX[31:0] EBX[7:0] 18

- X 0 6 B X 07 18

- 3. Electrical Specifications 19

- 3.1.4 Unused Signals 21

- 3.2.2 Voltage Planes 22

- 3.2.3 Voltage Identification 23

- 3.2.4.1 Transition Region 24

- 3.2.4.2 Transition Time 24

- 3.2.4.3 Noise 25

- 3.4 Maximum Ratings 26

- 3.5 DC Specifications 26

- 3.6 AC Specifications 41

- IL25,max 45

- V2,V3 (max) 49

- V1,V3 (min) 49

- D0004-00 50

- D0006-02 51

- IH18,min 52

- IL18,max 52

- IHVTTPWR,min 52

- ILVTTPWR,max 52

- D0009-01 55

- V00102-00 56

- V00103-00 57

- Specifications 58

- Time Dependant Overshoot 60

- Time Dependant Undershoot 60

- Parameter Recommendation 63

- 5. Mechanical Specifications 65

- TOP VIEW BOTTOM VIEW 66

- PACKAGE KEEPOUT 66

- CAPACITOR AREA 66

- TOP VIEW BOTTOM VIEW 70

- 5.3 Signal Listings 73

- Thermal Specifications 80

- Power 81

- Unit Notes 81

- 6.1 Thermal Diode 82

- Configuration 83

- 8. Processor Interface 84

- BCLK, BCLK# (I) 85

- BERR# (I/O - AGTL) 85

- BINIT# (I/O - AGTL) 85

- BNR# (I/O - AGTL) 85

- 01 100 MHz 86

- 11 133 MHz 86

- VID[4:0] (O – Open-drain) 93

- VREF (Analog) 93

- VTTPWRGD (I – 1.25 V) 93

- 8.2 Signal Summaries 94

- A1. Introduction 96

- A2. Filter Specification 96

- A4. Comments 98

(80 pages)

(80 pages)

Comments to this Manuals