Intel BX80525KY500512 Datasheet Page 29

- Page / 112

- Table of contents

- BOOKMARKS

Rated. / 5. Based on customer reviews

Pentium

®

III Xeon™ Processor at 500 and 550 MHz

Datasheet

29

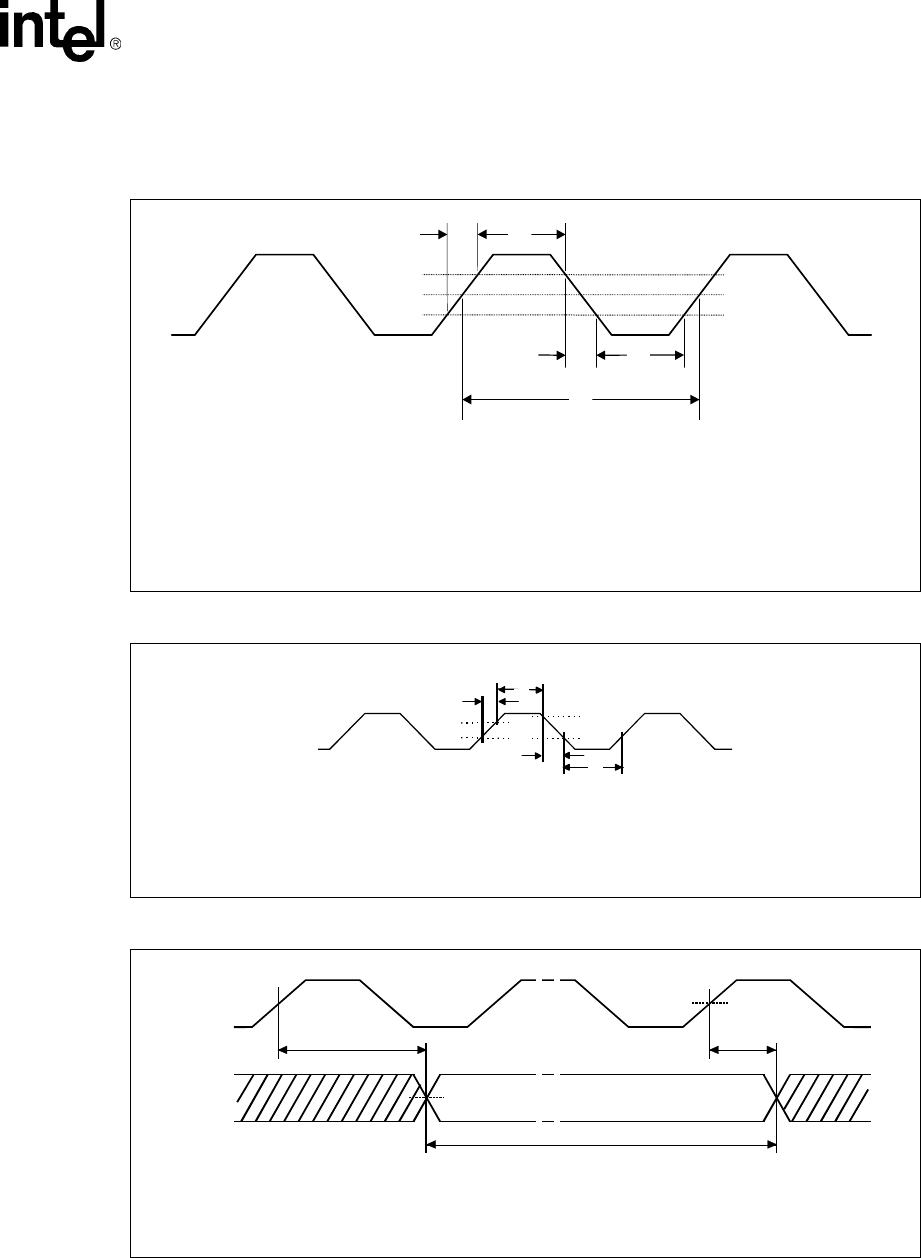

Figure 4 through Figure 12 are to be used in conjunction with the DC specification and AC timings

tables.

Figure 4. BCLK, PICCLK, TCK Generic Clock Waveform

Figure 5. SMBCLK Clock Waveform

Figure 6. Valid Delay Timings

1.25 V

0.5 V

2.0 V

T

p

T

f

T

r

Clock

T

h

T

l

T5, T25, T34 (Rise Time)

T6, T26, T36 (Fall Time)

T3, T23, T32 (High Time)

T4, T24, T33 (Low Time)

T1, T22, T31 (BCLK, PICCLK, TCK, Period)

T

r

=

T

f

=

T

h

=

T

l

=

T

p

=

SCLK

2.46V

0.84V

T

h

T

l

T

r

T

f

T

r

T54

T

f

T55

T52

T

h

T53

T

l

=

=

=

=

2.97V

0.84V

Clock

Signal

T

x

T

x

T

pw

V Valid Valid

T

x

T7, T11, T29 (Valid Delay)

=

T

pw

T14, T15 (Pulse Wdith)

=

V

2/3 V

TT

for GTL+ signal group; 1.25V for CMOS, and APIC signal groups=

- Product Features 1

- Datasheet 2

- Contents 3

- 1.0 Introduction 9

- 1.2 References 10

- 2.0 Electrical Specifications 11

- 2.2 Power and Ground Pins 12

- 2.3 Decoupling Guidelines 12

- 2.4.1 Mixing Processors 15

- 2.5 Voltage Identification 16

- 2.7 System Bus Signal Groups 18

- 2.9 Maximum Rating 20

- 1.0 4.0 ns 8 2 27

- 3.0 Signal Quality 32

- 4.0 Processor Feature 36

- 4.2.1 Normal State— State 1 37

- STPCL K# Asserted 38

- STPCL K# De-asserted 38

- 4.2.5 Sleep State — State 5 39

- 4.2.6 Clock Control 39

- 4.3.2 Scratch EEPROM 42

- # of Bit Function Notes 42

- Transactions 43

- 4.3.4 Thermal Sensor 43

- 4.3.6.3 Status Register 46

- 4.3.7 SMBus Device Addressing 48

- 5.1 Thermal Specifications 50

- .003/1.00x1.00 51

- Technique for Measuring T 54

- with 0° Angle Attachment 54

- with 90° Angle Attachment 54

- 6.0 Mechanical Specification 55

- 6.1 Weight 60

- .168 ± .021 61

- 6.3 Pentium 62

- Signal Listing 62

- 7.1 Introduction 71

- 7.2 Mechanical Specifications 71

- Thermal Specifications 74

- 8.0 Integration Tools 78

- 8.1.1 Primary Function 79

- 8.1.4 Debug Port Signal Notes 82

- 8.1.4.2 Signal Note: DBRESET# 83

- 8.1.4.4 Signal Note: TCK 83

- 9.0 Appendix 86

- 9.1.14 CPU_SENSE 89

- 9.1.15 D[63:00]# (I/O) 89

- 9.1.23 FRCERR (I/O) 91

- 9.1.25 IERR# (O) 91

- 9.1.26 IGNNE# (I) 91

- 9.1.27 INIT# (I) 92

- 9.1.28 INTR - see LINT0 92

- 9.1.29 LINT[1:0] (I) 92

- 9.1.30 LOCK# (I/O) 92

- 9.1.40 REQ[4:0]# (I/O) 94

- 9.1.41 RESET# (I) 94

- 9.1.42 RP# (I/O) 95

- 9.1.43 RS[2:0]# (I) 95

- 9.1.44 RSP# (I) 95

- 9.1.45 SA[2:0] (I) 95

- 9.2 Signal Summaries 98

- Table 49. Input Signals 99

- Datasheet 106

(112 pages)

(112 pages)

Comments to this Manuals